x86->4. 中断和动态时钟显示

中断和动态时钟显示

中断

为了最高效地利用cpu性能,中断将发生在程序之间来回切换的情况。中断分为外中断和内中断。

外中断

有非屏蔽中断(NMI)和可屏蔽中断(INTR),通过一根信号线传入对应的芯片引脚。

INTEL规定,NMI信号从0到1后,至少要维持4个始终周期才能被识别。在处理器内不可屏蔽,但在处理器外有NMI的开关。它的触发往往代表着致命的错误,以至于不得不停止所有工作。它的中断号为2,不再进行细分。

对于可屏蔽中断INTR,需要区分中断的类型和来源,因此它需要一个中断处理芯片。INTEL处理器规定的中断号为0~255,而8086使用的8259芯片负责提供其中的15个,但并不固定。软件编写的时候可根据需要访问处理芯片的端口号,用in或out指令改变状态。多年来设备不断更迭,但中断代理芯片的引脚0始终和实时时钟芯片rtc链接。

中断能否被处理,也和IF标志位有关。IF为0时,所有INTR都会被忽略。IF可以通过cli和sti指令改变

中断执行

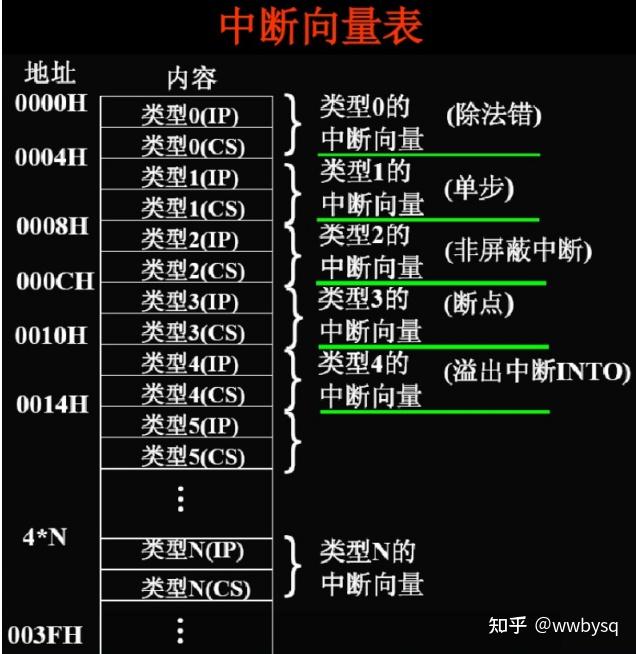

首先引入中断向量表

中断向量表在内存中保存,其中存放着 256个中断源所对应的中断处理程序的入口地址,因而用预制的程序处理中断将成为可能。

综合书中内容和https://blog.csdn.net/weixin_42240667/article/details/105071373

中断处理的基本过程包括中断请求、中断判优、中断响应、中断服务 和中断返回等五个阶段。下面的总结忽略请求阶段。

中断处理如下:(当中断请求已经发生且允许cpu响应中断时)

- 8259芯片判定优先级,把中断号传给cpu(中断判优)

- 进入中断响应阶段:

- 保护硬件现场

- 关中断

- 保护断点(压栈cpu中几个关键寄存器,即flags、清楚IF和TF位、在压栈cs和ip)

- 获得中断服务程序的入口地址

- 执行中断服务程序,当if被清除时,处理器不能响应硬件中断,但中断服务程序可在恰当时机再次sti指令打开中断

- 完成服务程序后,恢复现场,从栈中弹出执行状态,返回原来的断点继续执行程序(中断返回),是中断响应的逆过程。

时钟和cmos ram

早期的rtc芯片和接口都是独立焊接在主板上,现在则集成在ICH(外围设备控制器芯片)内部。其中有着cmos ram一小块存储日期、时间和计算机配置信息的存储器。rtc芯片由晶振驱动,对cmos ram进行每秒一次的刷新。访问cmos ram可通过两个端口0x70/0x74和0x71/0x75。

访问到的数据以BCD编码存储,即二进制存储十进制数,每四位不能超过1001